Введение в архитектуру cortex-m3. часть 2

Содержание:

- Стандартная часть

- x86 – главный соперник

- Debugging tools

- Микроконтроллеры Cortex-M0/M3/M4

- Особенности процессоров NVIDIA, TI, Qualcomm, Marvell

- Cortex-M Reference Manuals

- Using this template

- ARM big.LITTLE

- Item acquisition

- Development toolchains

- Первый спарринг

- Примечания

- Cortex-M4

- Роль CPU и GPU от ARM на рынке

- Заключение

Стандартная часть

Заголовочный файл предоставляет интерфейс к ядру. Для stm32f103c8 это , так как он работает на Cortex-M3. Для Cortex-M0+ это будет файл .

Под интерфейсом понимается удобный доступ к его регистрам. Например, в состав ядра входят еще две сущности: системный таймер и контроллер прерываний NVIC. Поэтому в этом файле содержатся вспомогательные функции для их быстрой настройки. Включить прерывание можно вызовом функции:

xxxxxxxxxx

static __INLINE void NVIC_EnableIRQ(IRQn_Type IRQn) {

NVIC->ISER = (1 << ((uint32_t)(IRQn) & 0x1F));

}

Вам не нужно работать с регистрами ядра напрямую.

Другие файлы нам не столь интересны, но справедливости ради упомянем их. Например файл содержит обертки инструкций, а — обертки некоторых важных системных функций.

xxxxxxxxxx

__attribute__( ( always_inline ) ) static __INLINE uint32_t __get_PSP(void) {

register uint32_t result;

__ASM volatile ("MRS %0, psp\n" : "=r" (result) );

return(result);

}

Если вы не разрабатываете приложение на самом низком уровне, то заглядывать в эти файлы незачем. Тем не менее, подробное описание работы ядра можно найти в документе ARM — Cortex-M3 Devices Generic User Guide, и мы им даже воспользуемся при настройке системного таймера.

x86 – главный соперник

х86 – представитель CISC-архитектур. В них используется полный набор команд. Одна инструкция в данном случае выполняет несколько низкоуровневых операций. Программный код, в отличие от ARM, компактнее, но выполняется не столь быстро и требует больших ресурсов. Кроме того, с самого начала х86 оснащались всеми необходимыми блоками, что предполагало как их универсальность, так и прожорливость. Дополнительная энергия тратилась на безусловное, параллельное выполнение команд. Это позволяет достичь преимущества в скорости, но некоторые операции при этом выполняются вхолостую, так как не удовлетворяют предыдущим условиям.

Такими были классические х86, но, уже начиная с 80486, Intel де-факто создала внутреннее RISC-ядро, которое выполняло CISC-инструкции, предварительно разложенные на более простые команды. Такую же конструкцию имеют современные процессоры Intel и AMD.

Debugging tools

JTAG and/or SWD debug interface host adapters (in alphabetical order):

- CMSIS-DAP by mbed.

- Crossconnect by Rowley Associates.

- DSTREAM by ARM Ltd.

- Green Hills Probe and SuperTrace Probe.

- iTAG by iSYSTEM.

- I-jet by IAR.

- Jaguar by Crossware.

- J-Link by SEGGER Supports JTAG and SWD. Supports ARM7, ARM9, ARM11, Cortex-A, Cortex-M, Cortex-R, Renesas RX, Microchip PIC32. Eclipse plug-in available. Supports GDB, RDI, Ozone debuggers.

- J-Trace by SEGGER. Supports JTAG, SWD, and ETM trace on Cortex-M.

- JTAGjet by Signum.

- LPC-LINK by Embedded Artists (for NXP) This is only embedded on NXP LPCXpresso development boards.

- LPC-LINK 2 by NXP. This device can be reconfigured to support 3 different protocols: J-Link by SEGGER, CMSIS-DAP by ARM, Redlink by Code Red.

- Multilink debug probes, Cyclone in-system programming/debugging interfaces, and a GDB Server plug-in for Eclipse-based ARM IDEs by PEmicro.

- OpenOCD open source GDB server supports a variety of JTAG probes OpenOCD Eclipse plug-in available in GNU ARM Eclipse Plug-ins.

- AK-OPENJTAG by Artekit (Open JTAG-compatible).

- AK-LINK by Artekit.

- RLink by Raisonance.

- ST-LINK/V2 by STMicroelectronics The ST-LINK/V2 debugger embedded on STM32 and development boards can be converted to SEGGER J-Link protocol.

- TRACE32 Debugger and ETM/ITM Trace by Lauterbach.

- ULINK by Keil.

Debugging tools and/or debugging plug-ins (in alphabetical order):

- GNU ARM Eclipse J-Link Debugging plug-in.

- GNU ARM Eclipse OpenOCD Debugging plug-in.

- Memfault Error Analysis for post mortem debugging

- Percepio Tracealyzer, RTOS trace visualizer (with Eclipse plugin).

- SEGGER SystemView, RTOS trace visualizer.

Микроконтроллеры Cortex-M0/M3/M4

Микроконтроллеры Cortex-M стали сегодня одними из самых популярных процессоров, применяемых при разработке и изготовлении электронной техники. Высокая вычислительная мощность, широкий набор периферии и низкая стоимость делают эти устройства привлекательными для самого широкого круга разработчиков. При этом каждый желающий может выбрать наиболее подходящий вариант для решения конкретной задачи. Производители предлагают огромное количество разнообразных микросхем, общим для которых остается только процессорное ядро. На сегодняшний день распространение получили 3 варианта ядер: Cortex-M0, Cortex-M3, Cortex-M4. Отличия этих моделей не всегда явно прослеживаются, поэтому данная статья делает попытку разобраться в особенностях этих вариантов.

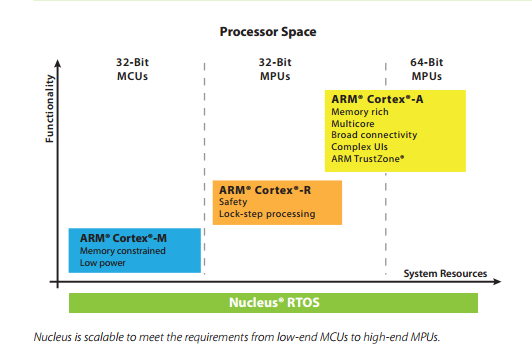

Микроконтроллеры Cortex-M представляют собой одно из направлений развития микропроцессорных ядер, предлагаемых фирмой ARM. Фактически, под общей торговой маркой Cortex можно увидеть три типа процессоров (профилей), обозначаемых буквами A, R, M. Задачей профиля A стало достижение большой вычислительной мощности. Изделия с этой маркировкой — Cortex-A, представляют собой классические микропроцессоры, являющиеся дальнейшей эволюцией разработок ARM. Профиль R нацелен на использование во встраиваемых системах, поэтому эти процессоры модернизированы для исполнения задач в реальном времени. Основной задачей профиля M заявлена простота и низкая стоимость. Технически Cortex-M представляют сильно упрощенные варианты старших моделей. Тем не менее, даже такие «урезанные» контроллеры обладают вычислительной мощностью, значительно превышающей многие аналоги. Также отличием от «больших» ARM стала поддержка битовых операций, необходимая в микроконтроллерах для работы с периферией.

Особенности процессоров NVIDIA, TI, Qualcomm, Marvell

Лицензируя ARM направо и налево, разработчики усиливали позиции своей архитектуры за счет компетенций партнеров. Классическим примером в данном случае можно считать NVIDIA Tegra. Эта линейка систем-на-чипе имеет в основе архитектуру ARM, но у NVIDIA уже были свои весьма серьезные наработки в области трехмерной графики и системной логики.

NVIDIA Tegra

ARM дает своим лицензиарам широкие полномочия по переработке архитектуры. Соответственно инженеры NVIDIA получили возможность совместить в Tegra сильные стороны ARM (вычисления CPU) и собственной продукции – работа с трехмерной графикой и т.д. В результате Tegra обладают высочайшей для своего класса процессоров производительностью в 3D. Они на 25-30% быстрее PowerVR, используемых Samsung и Texas Instruments, а также почти в два раза превосходят Adreno, разработку Qualcomm.

Другие производители процессоров на базе архитектуры ARM усиливают те или иные дополнительные блоки, совершенствуют чипы, чтобы добиться более высоких частот и производительности.

Qualcomm Snapdragon

Например, Qualcomm не использует референсный дизайн ARM. Инженеры компании серьезно переработали его и назвали Scorpio – именно он лежит в основе чипов Snapdragon. Отчасти дизайн был переработан с целью освоения более тонких техпроцессов, чем предусмотрено стандартным IP ARM. В результате первые Snapdragon выпускались по нормам 45 нм, что обеспечило им более высокие частоты. А новое поколение этих процессоров с заявленными 2.5 ГГц и вовсе может стать самым быстрым среди аналогов на базе ARM Cortex-A9. Также Qualcomm применяет собственное графическое ядро Adreno, созданное на базе разработок, приобретенных у AMD. Так что в некотором роде Snapdragon и Tegra – враги на генетическом уровне.

Samsung Hummingbird

Samsung при создании Hummingbird также пошла по пути оптимизации архитектуры. Корейцы совместно с компанией Intrinsity изменили логику, благодаря чему сократилось количество инструкций необходимых для выполнения некоторых операций. Таким образом удалось выиграть 5-10% производительности. Кроме того, был добавлен динамический кэш второго уровня и мультимедийное расширение ARM NEON. В качестве графического модуля корейцы использовали PowerVR SGX540.

Процессор OMAP 4 производства Texas Instruments

Texas Instruments в новых сериях OMAP на базе архитектуры ARM Cortex-A добавила специальный модуль IVA, ответственный за ускорение обработки изображений. Он позволяет быстрее обрабатывать данные, поступающие с сенсора встроенной камере. Кроме того, он подключен к ISP и содействует ускорению видео. В OMAP также применяется графика PowerVR.

Apple A4

Apple A4 обладает большим кэшем в 512 Кбайт, в нем используется графика PowerVR, а само ARM-ядро построено на базе варианта архитектуры, переработанного Samsung.

Apple A5

Двухъядерный Apple A5, дебютировавший в iPad 2 в начале 2011 года, базируется на архитектуре ARM Cortex-A9, также, как и в предыдущий раз оптимизированной Samsung. По сравнению с А4 новый чип обладает удвоенным объемом кэш-памяти второго уровня — его увеличили до 1 Мбайт. Процессор содержит двухканальный контроллер оперативной памяти, обладает улучшенным видеоблоком. В результате его производительность в некоторых задачах вдвое выше, чем у Apple A4.

Marvell предлагает чипы на базе собственной архитектуры Sheeva, которая при ближайшем рассмотрении оказывается гибридом XScale, некогда купленной у Intel, и ARM. Данные чипы обладают большим по сравнению с аналогами объемом кэш-памяти, снабжены специальным мультимедийным модулем.

Сейчас лицензиаты ARM производят только чипы на базе архитектуры ARM Cortex-A9. При этом, хотя она и позволяет создавать четырехъядерные варианты, NVIDIA, Apple, Texas Instruments и другие пока ограничиваются моделями с одним или двумя ядрами. Кроме того, чипы работают на частоте до 1.5 ГГц. Cortex-A9 позволяет делать двухгигагерцовые процессоры, но опять же производители не стремятся быстро наращивать частоты — ведь пока рынку хватит и двухъядерников на 1.5 ГГц.

По-настоящему многоядерными должны стать процессоры на базе Cortex-A15, но они если и анонсированы, то на бумаге. Их появления в кремнии стоит ожидать в следующем году.

Современные процессоры лицензиатов ARM на базе Cortex-A9:

Cortex-M Reference Manuals

The Cortex-M Device Generic User Guides contain the programmers model and detailed information about the core peripherals and are available for:

- Cortex-M0 Devices Generic User Guide (Armv6-M architecture)

- Cortex-M0+ Devices Generic User Guide (Armv6-M architecture)

- Cortex-M3 Devices Generic User Guide (Armv7-M architecture)

- Cortex-M4 Devices Generic User Guide (ARMv7-M architecture)

- Cortex-M7 Devices Generic User Guide (Armv7-M architecture)

The Cortex-M23 and Cortex-M33 are described with Technical Reference Manuals that are available here:

- Cortex-M23 Technical Reference Manual (Armv8-M baseline architecture)

- Cortex-M33 Technical Reference Manual (Armv8-M mainline architecture)

CMSIS also supports the following Cortex-M processor variants:

- Cortex-M1 is a processor designed specifically for implementation in FPGAs (Armv6-M architecture).

- SecurCore SC000 is designed specifically for smartcard and security applications (Armv6-M architecture).

- SecurCore SC300 is designed specifically for smartcard and security applications (Armv7-M architecture).

- Cortex-M35P is a temper resistant Cortex-M processor with optional software isolation using TrustZone for Armv8-M.

Using this template

- Before we begin you need to identify some characteristics of the target

device as these will be used to configure the project:

-

The ARM core. e.g. Cortex-M3.

-

Does the ARM core include an FPU? Cortex-M4F and Cortex-M7F cores do.

-

How much Flash memory and RAM does the target device has? e.g. 256 KiB of

Flash and 32 KiB of RAM. -

Where are Flash memory and RAM mapped in the address space? e.g. RAM is

commonly located at address .

You can find this information in the data sheet or the reference manual of your

device.

In this example we’ll be using the STM32F3DISCOVERY. This board contains an

STM32F303VCT6 microcontroller. This microcontroller has:

-

A Cortex-M4F core that includes a single precision FPU

-

256 KiB of Flash located at address 0x0800_0000.

-

40 KiB of RAM located at address 0x2000_0000. (There’s another RAM region but

for simplicity we’ll ignore it).

- Instantiate the template.

$ cargo generate --git https://github.com/rust-embedded/cortex-m-quickstart Project Name: app Creating project called `app`... Done! New project created /tmp/app $ cd app

- Set a default compilation target. There are four options as mentioned at the

bottom of . For the STM32F303VCT6, which has a Cortex-M4F

core, we’ll pick the target.

$ tail -n6 .cargo/config

# Pick ONE of these compilation targets # target = "thumbv6m-none-eabi" # Cortex-M0 and Cortex-M0+ # target = "thumbv7m-none-eabi" # Cortex-M3 # target = "thumbv7em-none-eabi" # Cortex-M4 and Cortex-M7 (no FPU) target = "thumbv7em-none-eabihf" # Cortex-M4F and Cortex-M7F (with FPU)

- Enter the memory region information into the file.

$ cat memory.x

/* Linker script for the STM32F303VCT6 */

MEMORY

{

/* NOTE 1 K = 1 KiBi = 1024 bytes */

FLASH : ORIGIN = 0x08000000, LENGTH = 256K

RAM : ORIGIN = 0x20000000, LENGTH = 40K

}

- Build the template application or one of the examples.

$ cargo build

ARM big.LITTLE

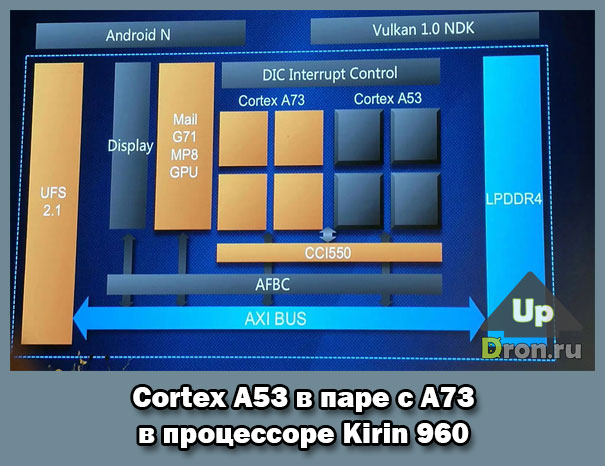

ARM big.LITTLE

В качестве высокотехнологичного решения проблемы энергопотребления современных процессоров ARM предлагает технологию big.LITTLE, суть которой заключается в объединении на одном чипе ядер различных типов, как правило, одинакового количества энергосберегающих и высокопроизводительных.

Существует три схемы работы ядер различного типа на одном чипе: big.LITTLE (миграция между кластерами), big.LITTLE IKS (миграция между ядрами) и big.LITTLE MP (гетерогенный мультипроцессинг).

big.LITTLE (миграция между кластерами)

Первым чипсетом на архитектуре ARM big.LITTLE стал процесссор Samsung Exynos 5 Octa. В нём используется оригинальная схема big.LITTLE “4+4”, что означает объединение в два кластера (отсюда и название схемы) на одном кристалле четырёх высокопроизводительных ядер Cortex-A15 для ресурсоёмких приложений и игр и четырёх энергосберегающих ядер Cortex-A7 для повседневной работы с большинством программ, причём в один момент времени могут работать ядра только одного типа. Переключение между группами ядер происходит практически мгновенно и незаметно для пользователя в полностью автоматическом режиме.

big.LITTLE IKS (миграция между ядрами)

Более сложная реализация архитектуры big.LITTLE — объединение нескольких реальных ядер (как правило двух) в одно виртуальное, управляемое ядром операционной системы, которое решает, какие задействовать ядра — энергоэффективные или производительные. Разумеется, виртуальных ядер также несколько — на иллюстрации приведен пример схемы IKS, где в каждом из четырёх виртуальных ядер находятся по одному ядру Cortex-A7 и Cortex-A15.

big.LITTLE MP (гетерогенный мультипроцессинг)

Схема big.LITTLE MP является наиболее “продвинутой” — в ней каждое ядро является независимым и может включаться ядром ОС по необходимости. Это значит, что если используются четыре ядра Cortex-A7 и столько же ядер Cortex-A15, в чипсете, построенном на архитектуре ARM big.LITTLE MP, смогут работать одновременно все 8 ядер, даже несмотря на то, что они разных типов. Одним из первых процессоров такого типа стал восьмиядерный чип компании Mediatek — MT6592, который может работать на тактовой частоте 2 ГГц, а также записывать и воспроизводить видео в разрешении UltraHD.

Будущее

По имеющейся на данный момент информации, в ближайшее время ARM совместно с другими компаниями планирует наладить выпуск big.LITTLE чипов следующего поколения, которые будут использовать новые ядра Cortex-A53 и Cortex-A57. Кроме того, бюджетные процессоры на ARM big.LITTLE собирается выпускать китайский производитель MediaTek, которые будут работать по схеме “2+2”, то есть, использовать две группы по два ядра.

Item acquisition

This map can only drop from maps Tier 14 or higher. It may also be sold by Zana or offered as her .

Upgrade paths

This item can be acquired through the following upgrade paths or vendor recipes:

| Amount | Ingredient | GeneralNotes | Type |

|---|---|---|---|

| 8 | The Encroaching DarknessThe Encroaching Darkness8MapCorruptedNo matter where your dreams take you, Nightmare follows close behind. | random corrupted Map | Automatic |

| 8 | Otherworldly IncubatorOtherworldly IncubatorAdds an incubated Unique Map item to an equippable itemItem drops after killing %1% monstersUnique Map ItemRight click this item then left click an item to apply it. The Incubated item drops after killing a specific number of monsters. | random Map | Automatic |

| 4 | Jack in the BoxJack in the Box4ItemTurn the crank, close your eyes, and pray to the gods for a pleasant surprise. | random item | Automatic |

Development toolchains

IDE, compiler, linker, debugger, flashing (in alphabetical order):

- Ac6 System Workbench for STM32 (based on Eclipse and the GNU GCC toolchain with direct support for all ST-provided evaluation boards, Eval, Discovery and Nucleo, debug with ST-LINK)

- ARM Development Studio 5 by ARM Ltd.

- Atmel Studio by Atmel (based on Visual Studio and GNU GCC Toolchain)

- Code Composer Studio by Texas Instruments

- CoIDE by CooCox(note — website dead since 2018)

- Crossware Development Suite for ARM by Crossware

- CrossWorks for ARM by Rowley

- Dave by Infineon. For XMC processors only. Includes project wizard, detailed register decoding and a code library still under development.

- DRT by SOMNIUM Technologies. Based on GCC toolchain and proprietary linker technology. Available as a plugin for Atmel Studio and an Eclipse-based IDE.

- Eclipse as IDE, with GNU Tools as compiler/linker, e.g. aided with GNU ARM Eclipse plug-ins

- EmBitz (formerly Em::Blocks) – free, fast (non-eclipse) IDE for ST-LINK (live data updates), OpenOCD, including GNU Tools for ARM and project wizards for ST, Atmel, EnergyMicro etc.

- emIDE by emide – free Visual Studio Style IDE including GNU Tools for ARM

- GNU ARM Eclipse – A family of Eclipse CDT extensions and tools for GNU ARM development

- GNU Tools (aka GCC) for ARM Embedded Processors by ARM Ltd – free GCC for bare metal

- IAR Embedded Workbench for ARM by IAR

- ICC by ImageCraft

- Keil MDK-ARM by Keil

- LPCXpresso by NXP (formerly Red Suite by Code Red Technologies)

- MULTI by Green Hills Software, for all Arm 7, 9, Cortex-M, Cortex-R, Cortex-A

- Ride and RKit for ARM by Raisonance

- SEGGER Embedded Studio for ARM by SEGGER.

- SEGGER Ozone by SEGGER.

- STM32CubeIDE by ST — Combines STCubeMX with TrueSTUDIO into a single Eclipse style package

- Sourcery CodeBench by Mentor Graphics

- TASKING VX-Toolset by Altium

- TrueSTUDIO by Atollic

- Visual Studio by Microsoft as IDE, with GNU Tools as compiler/linker – e.g. supported by VisualGDB

- VXM Design’s Buildroot toolchain for Cortex. It integrates GNU toolchain, Nuttx, filesystem and debugger/flasher in one build.

- winIDEA/winIDEAOpen by iSYSTEM

- YAGARTO – free GCC (no longer supported)

- Code::Blocks (EPS edition) (debug with ST-LINK no GDB and no OpenOCD required)

- IDE for Arduino ARM boards

- Arduino – IDE for Atmel SAM3X (Arduino Due)

- Energia – Arduino IDE for Texas Instruments Tiva and CC3200

Notes:

- Only for STM32 microcontrollers.

- Only for Atmel processors.

- Only for Texas Instruments processors.

- Only for NXP processors.

- Support «out of the box» only for compatible processors.

Первый спарринг

Главным соперником ARM со стороны х86 является Intel Atom, а теперь к ним можно прибавить еще и платформу AMD Brazos. Сравнение х86 и ARM провёл Вэн Смит, который создал тестовые пакеты OpenSourceMark, miniBench и один из соавторов SiSoftware Sandra. В «забеге» приняли участие Atom N450, Freescale i.MX515 (Cortex-A8), VIA Nano L3050. Частоты чипов х86 были снижены, но у них все равно оставалось преимущество за счет более совершенной памяти.

Результаты оказались весьма интересными. ARM-чип оказался также быстр, как и конкуренты в целочисленных операциях, при этом расходуя меньше энергии. Здесь нет ничего удивительного. Изначально архитектура была и достаточно быстрой и экономичной. В операциях с плавающей точкой ARM уступила х86. Здесь сказался традиционно мощный блок FPU, имеющийся у чипов Intel и AMD. Напомним, что в ARM он появился относительно недавно. Задачи, ложащиеся на FPU, занимают в жизни современного пользователя значительно место – это игры, кодирование видео и аудио, другие потоковые операции. Конечно, тесты, проведенные Вэном Смитом, сегодня уже не так актуальны. ARM значительно усилила слабые стороны своей архитектуры в версиях Cortex-A9 и особенно Cortex-A15, которая, например, уже может выполнять инструкции безусловно, распараллеливая решение задач.

Примечания

- (PDF) (недоступная ссылка) (2003). Дата обращения 6 января 2011.

- ARM Ltd and ARM Germany GmbH. . Keil. Дата обращения 6 января 2011.

- . ARM (2011). Дата обращения 6 января 2011.

- . Arm.com. Дата обращения 18 апреля 2009.

- . ARM. Дата обращения 12 декабря 2010.

- ↑ (недоступная ссылка). Дата обращения 14 октября 2014.

- ARM Holdings (19 March 2007).. Пресс-релиз. Проверено 11 April 2007.

- . ARM product website. Дата обращения 11 апреля 2007.

- ↑

- ↑

- . ARM Holdings. Дата обращения 13 октября 2012.

- . ARM Holdings. Дата обращения 13 октября 2012.

- . ARM Holdings. Дата обращения 13 марта 2016.

- . download.intel.com. Intel (May 2007). Дата обращения 2 декабря 2010.

- ↑

- Lal Shimpi, Anand . AnandTech (15 September 2012). Дата обращения 15 сентября 2012.

Cortex-M4

Вариант микроконтроллерного ядра Cortex-M4, по сравнению с Cortex-M3, не характеризуется ростом общих показателей. Фактически M4 тот же самый M3, но дополнительно оснащенный DSP-инструкциями. Наличие последних существенно ускоряет обработку потоковых данных, что в свою очередь делает M4 весьма привлекательным для использования в системах управления и обработки информации.

Возможности DSP, входящего в состав M4, позволяют параллельно выполнять четыре операции сложения/вычитания для 8-ми разрядных чисел или две операции сложения/вычитания с16-ти разрядными операндами. Также реализовано умножение за один цикл, при этом для 16-ти разрядных чисел возможно параллельное исполнение двух операций.

В серии M4 есть еще один вариант, под обозначением Cortex-M4F. В нем, дополнительно к DSP, установлен блок операций для чисел с плавающей точкой – FPU.

Кроме вышеназванных, существуют и другие варианты процессоров. Большинство из них представляют модернизированные варианты основных ядер. Несколько особняком стоит малоизвестный Cortex-M1, предназначенный для использования в программируемых логических матрицах. Основные характеристики этого процессора практически совпадают с вариантом M0, но при этом он реализован только в виде программной модели.

В отличие от профиля А, Cortex-M развивается не столь бурно. Когда и какими будут будущие микроконтроллеры неизвестно. Можно только предположить, что развитие пойдет по пути «больших» систем и в скором времени привычными станут двух-, трех или четырехядерные контроллеры.

You have no rights to post comments

Роль CPU и GPU от ARM на рынке

Несмотря на то, что компания ARM является автором и разработчиком одноимённой архитектуры, которая, повторимся, сейчас используется в подавляющем большинстве мобильных процессоров, её решения в виде ядер и графических ускорителей не пользуются популярностью у крупных производителей смартфонов. К примеру, справедливо считается, что флагманские коммуникаторы на Android OS должны иметь процессор Snapdragon с ядрами Krait и графический ускоритель Adreno от Qualcomm, чипсеты этой же компании используются в смартфонах на Windows Phone, а некоторые производители гаджетов, к примеру, Apple, разрабатывают собственные ядра. Почему же в настоящее время сложилась именно такая ситуация?

Возможно, часть причин может лежать глубже, но одна из них — отсутствие чёткого позиционирования CPU и GPU от ARM среди продуктов других компаний, вследствие чего разработки компании воспринимаются как базовые компоненты для использования в устройствах B-брендов, недорогих смартфонах и создания на их основе более зрелых решений. К примеру, компания Qualcomm почти на каждой своей презентации повторяет, что одной из её главных целей при создании новых процессоров является уменьшение энергопотребления, а её ядра Krait, будучи доработанными ядрами Cortex, стабильно показывают более высокие результаты по производительности. Аналогичное утверждение справедливо и для чипсетов Nvidia, которые ориентированы на игры, ну а что касается процессоров Exynos от Samsung и A-серии от Apple, то они имеют свой рынок за счёт установки в смартфоны этих же компаний.

Вышесказанное совершенно не значит, что разработки ARM значительно хуже процессоров и ядер сторонних компаний, но конкуренция на рынке в конечном итоге идет покупателям смартфонов только на пользу. Можно сказать, что ARM предлагает некие заготовки, приобретая лицензию на которые, производители могут уже самостоятельно их доработать.

Заключение

Микропроцессоры на архитектуре ARM успешно завоевали рынок мобильных устройств благодаря низкому энергопотреблению и сравнительно большой вычислительной мощности. Раньше с ARM конкурировали другие RISC-архитектуры, например, MIPS, но сейчас у неё остался только один серьёзный конкурент — компания Intel с архитектурой x86, которая, к слову, хотя и активно борется за свою долю рынка, пока не воспринимается ни потребителями, ни большинством производителей всерьёз, особенно при фактическом отсутствии флагманов на ней (Lenovo K900 сейчас уже не может конкурировать с последними топовыми смартфонами на ARM-процессорах).

А как вы думаете, сможет ли кто-нибудь потеснить ARM, и как дальше сложится судьба этой компании и её архитектуры?

За предоставленную информацию благодарим 4pda.ru.