Умножитель/делитель частоты цифровых сигналов с rc-цепочкой в цепи обратной связи

Содержание:

Счетчик-делитель

Счетчик-делитель на 10, изображенный в нижней части рис. 11.31 выполняет несколько различных функций. На вход этого декадного счетчика поступают импульсы с частотой следования 10 Гц; на выходе имеем 1 Гц. Состояния четырех двоичных выходов счетчика 7493 связаны логической операцией И ЛИ-НЕ.

|

Счетчик-делитель на 10 с параллельным переносом 144. |

Счетчик-делитель может быть реализован и на D-трштерах.

|

Логическая структура двухразрядного сумматора К155ИМ2.| Временная диаграмма работы счетчика К155ИЕ2 при перемычке 12 — 01.| Временная диаграмма работы счетчика К155ИЕ4.| Временная диаграмма, работы, счетчика КД55ЙЕ1.| Временная диаграмма работы счетчика К. 155ИЕ5. |

Синхронный последовательный счетчик-делитель на двенадцать К155ИЕ4 ( см. рис. 1 — 61, в) выполнен на четырех JK-триг-герах, при этом внутренние соединения выполнены так, что обеспечиваются схемы деления на два, три, шесть, двенадцать. Счетчик имеет вход установки в нулевое состояние.

Счетчик-делитель регулятора ЦР-2Б аналогичен счетчику-делителю регулятора ЦР-2Б. Усилитель время-импульсных сигналов может быть контактного или бесконтактного типа.

|

Счетчик-делитель на 10 с устройством сброса. |

Работает счетчик-делитель следующим образом. Под действием счетных импульсов счетчик изменяет свое состояние от нулевого до десятого. Дешифратор и включенный на его выходе триггер при состоянии счетчика 1010 вырабатывают сигнал с нулевым уровнем на выходе Qs, которым все разряды счетчика до прихода одиннадцатого счетного импульса пег реводятся в нулевое состояние. Так, после десяти входных импульсов счетчик сбрасывает накопленный результат, возвращаясь в исходное положение.

|

Структурная схема счетчика делителя. |

Так как счетчик-делитель работает на основе двоичного кода, а шаговый делитель — на основе унитарного кода, то введена дополнительная схема для сочетания делителя счетчика с шаговым делителем. При помощи дополнительной схемы осуществляется переход от записи чисел в двоичном счетчике в прямом коде к записи в обратном коде ( и обратный переход) без передачи ложных импульсов на вход логической схемы управления шаговым двигателем.

Микросхема представляет собой высокочастотный счетчик-делитель с программируемым коэффициентом деления.

Микросхема представляет собой 11-разрядный управляемый счетчик-делитель частоты с произвольным коэффициентом деления.

Микросхема представляет собой 12-разрядный программируемый двоичный счетчик-делитель и предназначена для формирования временных последовательностей импульсов, управляемых внешним кодом. Стыкуется по выходам с ТТЛ и КМОП-схемами, а по входу — с КМОП-схемами.

Микросхемы представляют собой счетчик-делитель на восемь.

Микросхемы представляют собой счетчик-делитель на восемь.

Вы здесь

Главная › Инженеру-конструктору › 4. Полезные схемы для радиолюбителей

13. Предварительный делитель частоты

вс, 04/02/2006 — 13:51 — admin

Предварительный делитель частоты.

(Головач С., Радио, 1997, Ns11, с. 57, 58)

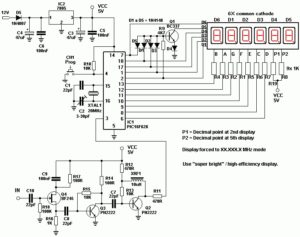

Частотомеры, выполненные в КМОП-технике, имеют существенный недостаток — предельная частота измерения не превышает в них, как правило, нескольких мегагерц*. Делитель частоты, принципиальная схема которого приведена на рис. 134, позволит значительно расширить частотный диапазон таких частотомеров.

На ЭСЛ-элементах DD1.1, DD1.2, переведенных в линейный режим работы резисторами R3 и R5, и транзисторе VT1 собран широкополосный усилитель-ограничитель (в ограничителе — диоды VD1, VD2) с коэффициен- том усиления-около 36. Делитель частоты выполнен на двух быстродействующих десятичных счетчиках DD2 (ЭСЛ) и DD3 (ТТЛ).

Форсированный запуск транзистора VT1 по базе и эмиттеру увеличивает крутизну фронтов низкочастотных сигналов и компенсирует спад усиления в DD1.1, DD1.2, начинающийся с 130…150 МГц.

Цепь питания каждой микросхемы должна быть заблокирована конденсатором емкостью 0,047 мкФ (на схеме не показаны).

В делителе можно применять любые резисторы и конденсаторы. Их номиналы могут отличаться от указанных на схеме на 20%. Переключатель SA1 — П2К.

Рис. 134. Делитель частоты 1:100, fmax=250 Мгц

Диоды должны быть германиевыми: вместо Д9Б подойдут любые из Д9, а также Д18, Д20, ГД507А; вместо Д311 — Д312 и Д310. Транзистор КТ326Б может быть заменен на КТ326БМ или любым из КТ337, КТ347, КТ363, КТ3109.

В усилителе-ограничителе можно использовать микросхемы К500ЛМ101, К500ЛМ102, К500ЛМ109.

Наладка делителя сводится к подбору резисторов R3 и R5. Подав на частотомер синусоидальный сигнал с частотой 1 МГц, амплитудой 100 мВ и контролируя сигналы на выходах элементов DD1.1, DD1.2 осциллографом, добиваются симметричного их ограничения.

Сопротивление резистора R1 должно быть равно волновому сопротивлению подводящего кабеля.

Основные параметры делителя

| Коэффициент деления | 1:100 |

| Полоса частот | 0,5…250 МГц |

| Чувствительность | 30 мВ |

| Входное сопротивление | 50; 75 Ом |

| Напряжение питания | 4,2…5,8 В |

| Потребляемый ток | 47 мА |

*) Становится высокочастотной и КМОП-техника. Так, в микросхемах серии КР1554 время переключения логического элемента составляет б… 10 нс, а максимальная частота сигналов на входах счетчиков, регистров, других автоматных микросхем может достигать 140 МГц (см. «Радио», 1995, № 9, с. 62).

Счётчики

Соединив последовательно несколько триггерных схем — делителей частоты на два, получим простейший многоразрядный двоичный делитель. Более общее название для делителей частоты — счетчики. Коэффициент деления счетчика, состоящего из n-триггеров типа Т, составляет 2n; здесь n — число двоичных разрядов счетчика. В настоящее время используется много вариантов счетных схем: асинхронные и синхронные; двоичные и десятичные; однонаправленные, только с увеличением счета, и двунаправленные, счет в которых может увеличиваться или уменьшаться (такие счетчики называют реверсивными). Коэффициент деления счетчика может быть либо постоянным, либо переключаемым.

Основой любой из этих схем служит линейка из нескольких триггеров. Рассмотренные варианты счетчиков различаются схемой управления этими триггерами. Между триггерами добавляются логические связи, назначение которых — запретить прохождение в цикле счета лишним импульсам, К примеру, четырехтриггерный счетчик может делить исходную частоту на 16, так как 24 = 16. Получим минимальный выходной код 0000, а максимальный 1111. Чтобы построить счетчик-делитель на 10, трех триггеров недостаточно (10 23), поэтому десятичный счетчик содержит в своей основе четыре триггера, но имеет обратные связи, останавливающие счет при коде 9 = 1001.

Таким обазом, удобно выпускать четырехтриггерные счетчики в двух вариантах: двоичном и десятичном. Примеры таких микросхем — пары: ИЕ6 и ИЕ7, ИЕ16 и ИЕ17. Расширять функции счетчиков можно; видоизменяя их цепи управления. Первоначально счетчики были асинхронными. В асинхронном режиме предыдущий триггер вырабатывает для последующего тактовые импульсы. Такие счетчики иногда называют счетчиками пульсаций.

В синхронном счетчике все триггеры получают тактовый импульс одновременно, поскольку тактовые входы их соединяются параллельно. Поэтому Триггеры переключатся практически одновременно. В счетчике пульсаций каждый триггер, вносит в процесс счета определенную задержку, поэтому младшие разряды результирующего кода появляются на выходах триггеров неодновременно, т. е. несинхронно с соответствующим тактовым импульсом. Например, для четырехразрядного счетчика пульсаций выходной параллельный код 1111 появится на выходах триггеров уже после того, как поступит шестнадцатый тактовый импульс, кроме того, эти четыре единицы сформируются неодновременно.

Синхронная схема значительно сложнее асинхронной. На ее выходах данные от каждого разряда появляются одновременно и строго синхронно с последним входным импульсом. В синхронный счетчик разрешается синхронная (с тактовым импульсом) параллельная (в каждый триггер) загрузка начальных данных. Триггерная линейка синхронного счетчика снабжается специальным шифратором, который называется схемой ускоренного переноса (СУП).

Внутренние логические элементы управления, которыми часто снабжаются счетчики, позволяют сделать процесс счета реверсивным. Согласно команде, подаваемой на вход управления счетом больше/меньше, можно либо, увеличивать либо уменьшать на единицу содержимое счетчика при каждом очередном тактовом импульсе. У некоторых счетчиков тактовые входы на увеличение и на уменьшение отдельные.

Сброс данных счетчика, чтобы на всех выходах установился нулевой код, у одних схем асинхронный R, у других синхронный SR, происходит одновременно е приходом тактового импульса. Имеются счетчики с переменным коэффициентом деления. Устанавливаемый коэффициент деления зависит от кода, набранного на входах управления.

Рассмотрим микросхемы КМОП среднего уровня интеграции, необходимых для счета импульсов и деления частот. Счетчики-делители составляют несколько групп. Например, счетчики ИЕ3 ИЕ5 предназначены для построения схем электронных секундомеров, часов, таймеров. Их можно использовать, например, для обслуживания индикаторов цифровых мультиметров, термометров. Счетчики ИЕ8 и ИЕ9 имеют дешифрованные выходы (10 и 8 соответственно). Счетчики ИЕ11 и ИЕ14 однотипные четырехразрядные, реверсивные. Разнообразные возможности деления частот открывает применение счетчиков выполненых на микросхемах КМОП: ИЕ2, ИЕ10, ИЕ16 и ИЕ19. Имеются счетчики асинхронные, синхронные, разрядные и даже 14-разрядный — ИЕ16.

Вы здесь

Главная › Справочные материалы › 1. Цифровые микросхемы › 4. Схемотехника узлов на МОП микросхемах

8. Деление частоты

сб, 04/01/2006 — 23:40 — admin

Деление частоты

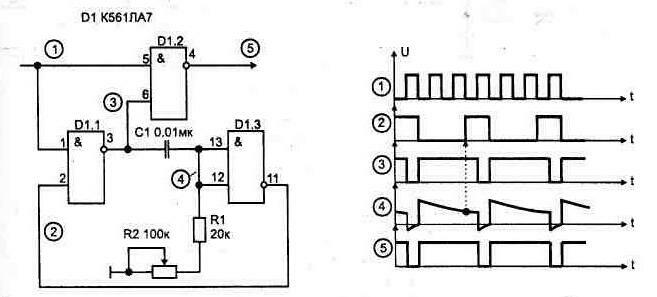

Наиболее часто для этого используют счетчики, хотя можно разделить частоту с помощью ждущего мультивибратора, ограничив число проходящих на выход импульсов. Пример такой схемы показан на рис. 1.60. Как только импульс входной частоты поступает на выход 5, ждущий мультивибратор D1.1, D1.3 запирает элемент D1.2 на время, определяемое резистором R1. Когда ждущий мультивибратор возвращается в исходное состояние, на выход поступает следующий импульс и цикл возобновляется. Схему можно усовершенствовать, заменив потенциометр полевым транзистором, что позволит управлять коэффициентом деления с помощью напряжения.

Рис. 1.60 Делитель частоты с использованием ждущего мультивибратора

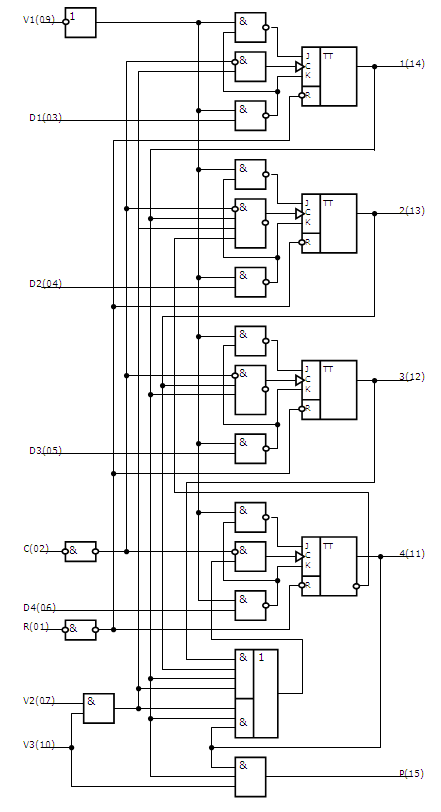

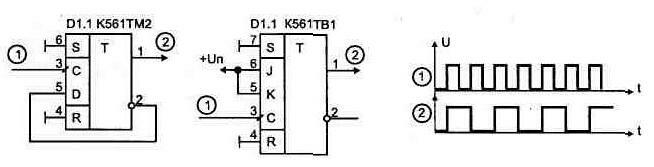

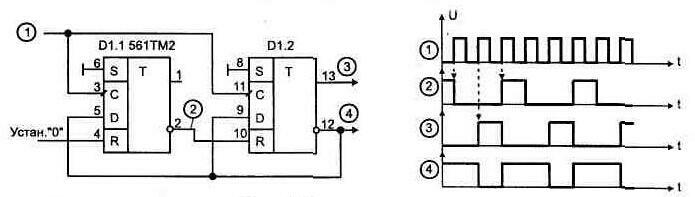

Делитель на 2 можно собрать из простейших ЛЭ, рис. 1.61. Схемы делителей без использования RC-цепей имеют лучшую помехоустойчивость и болееширокий диапазон входной частоты сигнала. Основным элементом всех счетчиков является триггер с так называемым счетным входом, рис. 1.62. Таблица 1.4

Таблица 1.4

|

Сигналы на входах |

Состояние выхода |

||||

|

С |

D |

S |

R |

Q |

NOT Q |

|

х |

х |

1 |

1 |

||

|

х |

х |

1 |

1 |

||

|

_/ |

1 |

||||

|

_/ |

1 |

1 |

|||

|

\_ |

х |

Q |

NOT Q |

Рис. 1.62. Делитель частоты на 2

Рис. 1.63. Делитель на 3

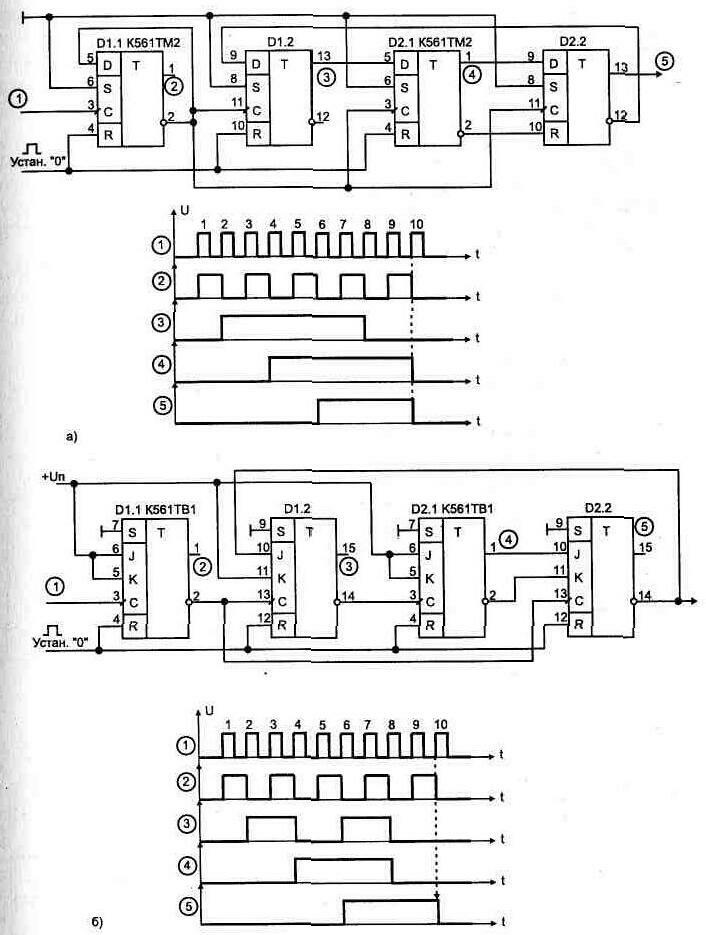

Рис. 1.64. а) Делитель на 10 на RS-триггерах; б) делитель на 10 на JK-триггерах

поясняет логику работы триггера 561ТМ2 в зависимости от управляющих сигналов (х — безразлично состояние на данном входе; состояние, когда на входах S и R микросхемы одновременно действует лог. «1», является запрещенным).

Комбинационное включение триггеров позволяет получать счетчик с нужным коэффициентом деления входной частоты. На рис. 1.63…1.65 приведены примеры включения элементов микросхем для получения деления на 2, 3, 6, 10 и 60.

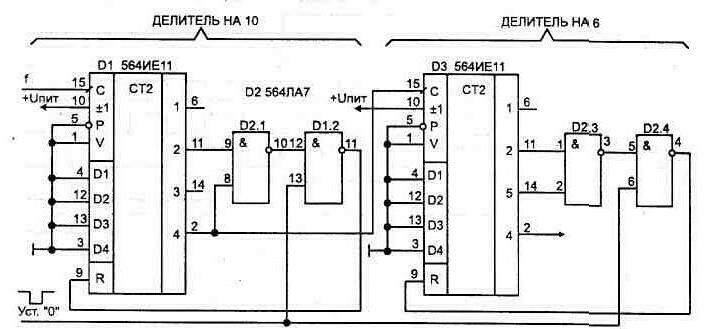

Промышленность выпускает универсальные счетчики, которые в зависимости от управляющих сигналов могут переключаться по переднему или заднему фронту входного сигнала, а также менять направление счета (сложение или вычитание). В качестве примера приведена диаграмма работы двоичного четырехразрядного реверсивного счетчика на микросхеме 561ИЕ11, рис. 1.66.

Таблица истинности (табл. 1.5) поясняет назначение управляющих сигналов и логику управления микросхемой (1 — лог. «1»; 0 — лог. «0»; х — состояние безразлично, т. е. 0 или 1). Счетчик предусматривает возможность загрузить по входам D1, D2, D4, D8 параллельный код.

Рис. 1 65. Схема делителя на 60

Таблица 1.5

|

Вход переноса РО |

Сложение, вычитание +-1 |

Разрешен. установки V |

Установка нуля R |

Действие |

|

1 |

х |

нет счета |

||

|

1 |

работа на сложение |

|||

|

работа на вычитание |

||||

|

х |

х |

1 |

установка по парал. вх. |

|

|

х |

х |

х |

1 |

установка нуля |

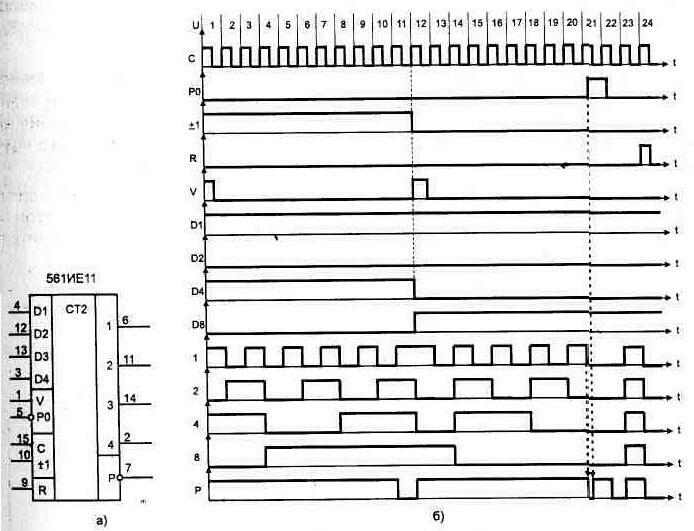

Для получения нужного коэффициента деления можно использовать микросхемы двоичных счетчиков, соединяя соответствующие выходы с помощью ЛЭ, рис. 1.67, или же применить счетчик с программируемым коэффициентом деления 564ИЕ15, см. рис. 1.26.

Рис. 1. 66. а) Универсальный реверсивный счетчик, б) диаграмма напряжении микросхемы

Pис 1.67. Делитель на 1000