Прошивка через jtag: схема, распиновка, инструкция

Содержание:

- Введение

- Эволюция отладочных средств на процессорах Intel

- Сервис и поддержка

- Технология

- JTAG Visualizer

- Identifying JTAG connector

- Работа с программатором

- JTAG automate

- Настройка

- Задействуем Eclipse

- JTAG software

- Зачем нужен JTAG

- JTAG прошивка по шагам

- JTAG в каждый дом: полный доступ через USB +57

- Инструкция на английском языке для восстановления мобильного устройства SAMSUNG GT-i9100, приведенная в RIFF JTAG менеджере

- Загрузка файла конфигурации в микросхему ПЛИС

Введение

Ранее мы рассказывали про методы снятия дампа памяти с мобильного телефона и его последующего анализа (статья «Снятие дампа памяти с мобильных устройств на Android»). Однако стандартные методы снятия дампа памяти не всегда помогают специалисту получить информацию с мобильного устройства. Это может быть вызвано следующими причинами:

- Устройство заблокировано паролем.

- Отсутствует возможность перевести мобильное устройство в режим для снятия дампа памяти.

- Некорректная работа операционной системы мобильного устройства или загрузчика.

- Повреждены компоненты мобильного устройства, отвечающие за взаимодействие пользователя с ним.

Поэтому одно из возможных решений проблемы — использовать сервисные разъемы на материнской плате мобильного устройства. JTAG — аппаратный интерфейс для прямой связи компьютера с материнской платой с помощью программаторов RIFF Box, Octopus и т. п. Стоит отметить, что некоторые программаторы создают дамп памяти мобильного устройства в собственном формате (отличном от RAW). В нашем случае мы связываем материнскую плату мобильного устройства с компьютером через программатор.

Эволюция отладочных средств на процессорах Intel

1. От in-circuit emulator к JTAGРис. 1. Intel I2ICE — один из первых внутрисхемных отладчиков для процессоров Intel 80386 (recycledgoods.com/intel-series-iv-emul-system-iii514b.html)Рис. 2. Объединение отлаживаемых устройств в JTAG-цепочку2. Режим зондовой отладки3. Современные аппаратные средства и технологии отладки процессоров Intel

- Intel In-Target Probe eXtended Debug Port (ITP-XDP) (рис.3);

- Intel Direct Connect Interface (DCI) — специализированная технология, которая предоставляет JTAG-интерфейс через порт USB 3.0. Существуют две возможности подключения (рис. 4):

Рис. 3. ITP-XDPРис. 4. Типы подключения DCIРис 5. Intel SVT Closed Chassis Adapter

Сервис и поддержка

Наши инженеры имеют богатый опыт работы на различных предприятиях и локализованы по всему миру. Обычно к вам прикрепляется определенный сервис инженер, который постоянно работает с вами. Этот инженер имеет за спиной большую группу поддержки. Посетите страницу Поддержка.

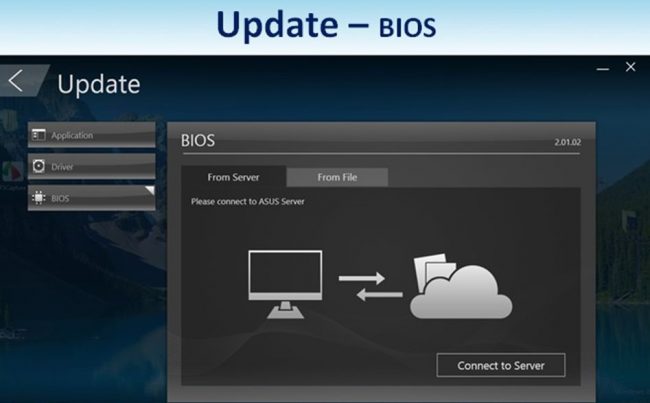

Все клиенты, пользующиеся платной годовой поддержкой, получают постоянные обновления программного обеспечения (через Интернет или почтовой доставкой). Например, JTAG ProVision доступен бесплатно для всех, кто имеет предыдущие (более примитивные) программные пакеты, но при этом имеет годовую поддержку. Кроме того, пользователи поддержки имеют доступ к защищенным областям web-сайта и имеют наивысший приоритет при сервисном обслуживании, пользуясь свободно услугами прикладных инженеров.

Свяжитесь с нами для более подробной информации.

Мы предлагаем обучающие курсы, которые будут соответствовать вашим потребностям. Обучение использованию JTAG ProVision и JTAG Visualizer требует всего пару дней. Обучение использованию производственных станций требует еще меньше времени – например половину дня. Больше об обучении.

Технология

Очень немного. Зачастую даже не требуется добавлять ничего лишнего. Однако иногда бывает полезно добавить несколько пассивных элементов для согласования каналов сканирования для увеличения максимальной частоты тестирования. Кроме того, вам понадобится вывести хотя бы один физический JTAG-разъем. Добавление некоторых коммутирующих микросхем может понадобиться, если вы собираетесь тестировать по одной JTAG-шине сложную систему из множества плат. Для получения поле подробных рекомендаций закажите печатную версию Руководства по тестопригодному проектированию плат.

В большинстве случаев, только небольшая часть микросхем на плате требует поддержки периферийного сканирования для создания полноценных тестов всей платы. Многие цифровые микросхемы (микропроцессоры, ПЛИС, ASIC и т.д.) являются довольно сложными и благодаря большому количеству выводов имеют доступ к большинству цепей на плате. Кроме того, использование специальных модулей ввода/вывода позволяет увеличить тестовое покрытие, например, при подключении их к внешним разъемам. Такие устройства, как память, тестируются не имея при этом JTAG-структуру. Тестовое покрытие платы легко рассчитать в программном пакете JTAG ProVision.

Изучите BSDL-файл на данную микросхему (обычно BSDL-файл находится в доступе на сайте производителя). Само наличие BSDL-файла уже говорит о том, что микросхема поддерживает стандарт периферийного сканирования. Также проверьте BSDL-файл на наличие ограничений по использованию сканирования в данном типе ИМС. Иногда требуется удержание некоторых выводов в статичном состоянии для обеспечения режима сканирования. При сомнениях обращайтесь в JTAG Technologies за советом.

Не существует специальных ограничений на количество JTAG-портов, которыми может управлять одновременно оборудование и ПО от JTAG Technologies. Во многих случаях разбивка микросхем с периферийным сканированием на отдельные каналы сканирования добавляет определенную гибкость при проектировании и тестировании плат, в частности, увеличивает время программирования флэш. Таким образом, мы не всегда рекомендуем использовать один канал сканирования для большого числа микросхем с JTAG. Для получения поле подробных рекомендаций закажите печатную версию Руководства по тестопригодному проектированию плат.

Нет ограничений для JTAG ProVision в том, сколько микросхем может быть объединено в одну JTAG-цепочку. Длина канала сканирования – это прежде всего длина тестовых векторов, которые будут сдвигаться в процессе JTAG-тестирования платы. Чем длиннее цепочка, тем длиннее тестовые векторы. Для получения поле подробных рекомендаций закажите печатную версию Руководства по тестопригодному проектированию плат. JTAG ProVision автоматически строит сложные цепочки сканирования из нескольких микросхем, так что можете смело объединять их.

JTAG Visualizer

Во время разработки вашего изделия и создания тестов инженеры могут использовать Visualizer для того, чтобы увидеть прогресс в достигнутом тестовом покрытии. Программа будет показывать им на электрической схеме, какие ее части могут быть протестированы при помощи периферийного сканирования, а какие – нет. Таким образом, разработчик может сделать упреждающие изменения в схемотехнике для достижения лучшего тестового покрытия даже еще до разводки платы. Visualizer может послужить фактором сбережения времени, отсекая необходимость в будущем проводить изменения в плате для достижения желаемой тестопригодности.

Второй очень значимый этап использования Visualizer – это проведение ремонта собранных плат или изделий, поступивших от потребителя, когда тесты при помощи периферийного сканирования уже проведены и получены результаты диагностики, показывающие дефекты в определенных цепях или выводах. Тогда при помощи Visualizer можно избежать поиска этих цепей на схеме, отправив в него результаты диагностики – не прошедшие цепи или компоненты подсветятся красным цветом.

Для отображения схематики в JTAG Visualizer у нас есть экстракторы для Cadence (Orcad), Mentor (все платформы) и Zuken CR-5000. Для топологии платы мы поддерживаем Cadence ODB++, Mentor (все платформы), Zuken CR-5000 и Cadif, Altium PCAD, DDE Supermax ECAD и Intercept Pantheon. Планируются дополнительные экстракторы.

Identifying JTAG connector

Headers

There are two major JTAG header arrangements used in SOHO routers based on MIPS CPUs. One uses 12 pins and the other uses 14 pins. While not radically different, you should be familiar with both. Other JTAG pinouts can be found at http://www.jtagtest.com/pinouts/.

8 Pin Header — 1 row

Common in Thomson routers, but not elsewhere. Specifically these are JST-SH-8, 1.0mm pitch. If you want a tidy connection rather than soldering wires directly to the board, Sparkfun stocks single cable/socket pairs (for their Arduino Mega Pro Mini), and bags of 10 cable assemblies and sockets are cheap on eBay. They still need to be hand-soldered as they don’t take too kindly to hot air tools.

Common in Thomson routers, but not elsewhere. Specifically these are JST-SH-8, 1.0mm pitch. If you want a tidy connection rather than soldering wires directly to the board, Sparkfun stocks single cable/socket pairs (for their Arduino Mega Pro Mini), and bags of 10 cable assemblies and sockets are cheap on eBay. They still need to be hand-soldered as they don’t take too kindly to hot air tools.

?1nTRST 2TCK 3TMS 4GND 5TDO 6TDI 7GND 8

10 Pin Header

Found in many Huawei routers:

TCK GND12TDO VREF34TMS nSRST56-nTRST78TDI GND910

It matches with the ALTERA ByteBlasterMV 10-pin cable, but without the nSRST, nTRST pins.

12 Pin Header

Found in Linksys routers such as the WRT54G and WRT54GS, the 12-pin header has the following arrangement of JTAG signals and pins:

nTRST GND12TDI GND34TDO GND56TMS GND78TCK GND910nSRST GND11 12

Seems, this header is a truncated version of the full EJTAG header.

14 Pin Header

This header is fully MIPS EJTAG 2.6 compatible and described in the EJTAG 2.6 standard. Found in Edimax routers (and other brands that are Edimax clones), the 14-pin header has the following arrangement of JTAG signals and pins:

nTRST GND12TDI GND34TDO GND56TMS GND78TCK GND910nSRST n/a11 12n/a Vcc13 14

A buffered cable such as the Wiggler requires an external Vcc voltage supply. The 14-pin header conveniently supplies this voltage on pin 14. The typical unbuffered cable, however, does not require an external voltage in order to function. Formally, the pin 14 is called VREF and used to indicate a JTAG signal levels: 5V, 3.3V or 2.5V. On the most devices this pin is tied to the device’s Vcc and may be used to power a buffer IC chip (and to generate an appropriate levels as result). Note that the 12-pin JTAG header arrangement does not provide Vcc.

16 Pin Header

Usually found in IBM 4XX powerpc platform, this layout is also known as JTAG RISCWATCH

TDO -12TDI nTRST34HALTED VREF56TCK -78TMS -910HALT GND11 12nSRST KEY13 14-GND15 16

20 Pin Header

Found in Comtrend routers:

nTRST GND12TDI GND34TDO GND56TMS GND78TCK GND910nSRST GND11 12Vcc ?13 14Vcc GND15 16Vcc GND17 18Vcc GND19 20

Not fully verified, Vcc at the bottom left are by add smd 0ohm.

JTAG pinout scan

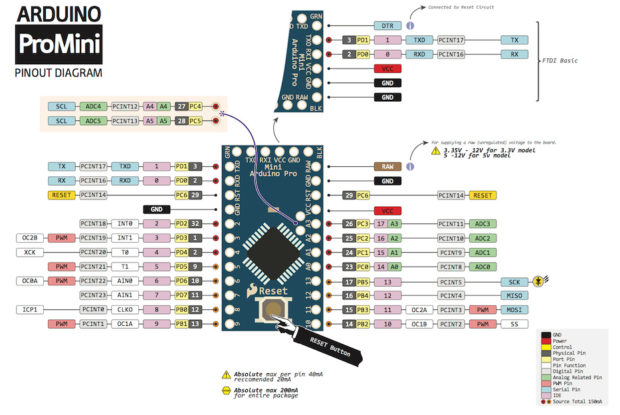

We can detect the pinout using a microcontroller like Arduino with specific software for this purpose. There are several implementations, probably JTAGenum is the best one.

JTAGenum

JTAGenum is opensource and runs over an Arduino board. It can find the JTAG pinout among a large amount of pins. The drawback is the 5V signal voltage level on most Arduino boards, whereas most routers use a 3.3V signal voltage levels. Therefore a level shift converter is required to wire the original Arduino with the test points at the router. Otherwise, there are some Arduino-compatible boards (like WeMos D1 for instance) built upon the famous ESP8266 which runs itself and the whole board at 3.3V, so you are ready to go on scanning JTAG headers of common consumer networking equipment.

Работа с программатором

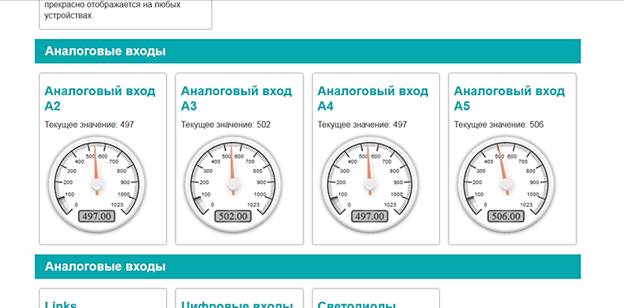

Немного о практике. Для проверки подключите к порту А 3 светодиода. Затем к плате подключается: четыре провода интерфейса (TCK, TDI, TMS, TDO) и 2 силовых Vcc идут на плюс, а GND подключается к земле. Всё, питание есть, можно идти дальше. В студии необходимо провести компиляцию кода и его запуск. Проект быстро скомпилируется, тут же будет прошит и начнёт работать. Чтобы следить за процессом исполнения, можно нажать F11, и тогда можно наблюдать, на каком ряду кода сейчас программа. Для этого достаточно поднести курсор к ряду, который включает светодиод, и он загорится. Существует ещё много экспериментов. Помните, что для того чтобы что-то сделать, необходимо работать. Пускай продвижение будет медленным, но со временем вы сможете получить именно то, что хотите, главное — не опускать руки и продолжать экспериментирование с упором на теоретическую базу (без неё никак).

JTAG automate

There is always a JTAG automate (JTAG logic) integrated into your soc or cpu and usually this is connected to a JTAG header on the PCB. You can test and program the IC by issuing to it through the JTAG.

To do that, you need to connect the parallel port of your PC with the JTAG header on the PCB via a bought or a homemade “JTAG cable”. You then run a special JTAG software on your PC, which allows you to comfortably control the JTAG automate and make it perform commands like reads and writes at arbitrary locations.

As already stated the primary intention of the JTAG automate is to test the IC itself. But of course it can additionally be utilized to recover a device if you erased the bootloader resident on the flash. Because, through the JTAG automate in the SoC, you can also write to the Flash Chip.

A JTAG port can be used without any software running on the IC itself, but the IC still has to be powered by a separate power supply. This means, you can solder a lonely SoC to a PCB, no Flash-Chip, no RAM; then connect to it via JTAG and interact with the SoC. Of course, on the PC itself, you should have some sort of software, to make this interaction with the hardware on the lowest level possible a bit more comfortable.

Of course, if there is a flash chip soldered onto the PCB, you could access this chip by programming the SoC via JTAG. It’s one of those amazingly useful things that allows you to recover from pretty much anything that doesn’t involve a hardware failure.

The JTAG automate is not a standardized system. Different SoCs/CPUs/ISAs have different JTAG automate behavior and reset sequence, most likely you will find ARM and MIPS CPUs, both having their standard to allow controlling the CPU behavior using JTAG.

Finding JTAG connector on a PCB can be a little easier than finding the UART since most vendors leave those headers unpopulated after production. JTAG connectors are usually 12, 14, or 20-pins headers with one side of the connector having some signals at 3.3V and the other side being connected to GND.

Настройка

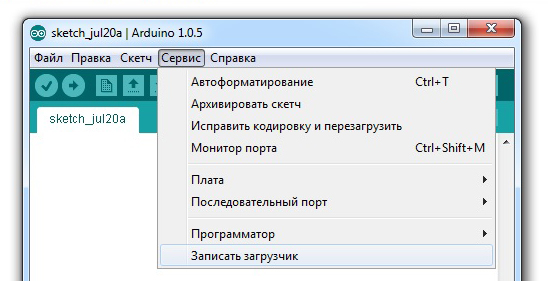

Учитывая, что есть необходимые схемы, следует только вытравить плату. Далее всё аккуратно подсоединяется, припаивается на места, и проверяется работа программатора путём прошивки загрузчика. Затем следует с AVR Studio обновить прошивку для JTAG-программатора до последней версии или до тех пор, пока надо. К адаптеру подключается программатор. Если он работает – значит можно переходить к следующему разделу, в котором обрисованы нюансы работы и программирования. Следует учесть, что все необходимые провода есть, они только нестандартно расположены.

В качестве подготовки к работе следует выставить Fuse биты. Они зависят от нотации, в которой производится работа. Для лучшего понимания представляем вот такую таблицу:

|

Бит |

Прямая нотация (Даташит, UniProf) |

Инверсная нотация (AVR DUDE GUI, PonyProg) |

|

OCDEN |

||

|

JTAGEN |

||

|

SPIEN |

||

|

CKOPT |

||

|

EESAVE |

||

|

BOOTSZ1 |

||

|

BOOTSZ0 |

||

|

BOOTRST |

||

|

BODLEVEL |

||

|

BODEN |

||

|

SUT1 |

||

|

SUT0 |

||

|

CKSEL3 |

||

|

CKSEL2 |

||

|

CKSEL1 |

||

|

CKSEL0 |

А как понять, какую выбрать? Ответ на вопрос прост: следует подключиться к микроконтроллеру и начать читать эти самые биты

Обратите внимание на SPIEN – если есть галочка напротив него, то это значит, что нотация инверсная. Если её нет – значит, она прямая

Если всё было сделано правильно, то программатор готов, чтобы прошивать микроконтроллеры. Но если он в последующем не сможет сделать прошивку – перечитайте и проверьте всё ещё раз.

Задействуем Eclipse

Тут есть целый ряд шагов, который прекрасно описан в , и я их не буду повторять.

Советы по отладке в Eclipse

-

Забудьте про кнопку EN аки reset на плате. Перезапуск делайте только через «Terminate and relaunch».

-

Для прошивки используйте

Можете добавить это как цель сборки, поставив кастомной командой, а в поле «имя цели» вписать аргументы (без кавычек).

-

Вы можете получить не то, что ожидали, после остановки и возобновления. Моя библиотека для воспроизведения звука после этого тараторит как ненормальная из-за приколов с таймером.

На этом мой текущий опыт работы с данной системой заканчивается. Желаю плодотворной отладки (будем честны, приятной она не бывает)!

JTAG software

Hairydairymaid

The most famous software for JTAG is probably the Linksys De-Brick Utility by Hairydairymaid (aka Lightbulb). As of 12 September 2006 the most recent version is v4.8. Virtually everyone who uses this software opts for an unbuffered cable, and the software itself, by default, expects this type of cable to be used.

There is source code available on GitHub at https://github.com/etmatrix/debrick_buspirate. The Github repo is likely the most stable source (the cshore site will not be hosting it any longer, as it was only added back for lack of another source).

The utility CAN operate on most any MIPS based cpu supporting EJTAG by using PrAcc routines (non-dma mode) — use the /nodma switch. It is not limited to WRT54G/GS units.

If you don’t have a PC with parallel port but instead own a Raspberry Pi, you can use a Raspberry Pi version of this software instead which uses to drive the JTAG lines.

Downloads:

zjtag-1.8.zip

Hairydairymaid variants:

-

tjtag-pi

-

tjtag-arduino

-

tjtag-arduigler-HID

-

zjtag

-

freetzlinux-wrtjp

- brjtag

- tjtag (AKA Tornado MOD)

UrJTAG

Another popular JTAG utility is Openwince JTAG. But is no longer developed. In late 2007, development of the openwince JTAG tools has been resumed in a new project named UrJTAG, with improvements like support for USB cables.

jtag> print No. Manufacturer Part Stepping Instruction Register --------------------------------------------------------------------------------------------- 0 Lexra LX5280 1 BYPASS BR Active bus: *0: EJTAG compatible bus driver via PrAcc (JTAG part No. 0) start: 0x00000000, length: 0x20000000, data width: 8 bit start: 0x20000000, length: 0x20000000, data width: 16 bit start: 0x40000000, length: 0x20000000, data width: 32 bit

OpenOCD

OpenOCD is more complex than Hairydairymaid or UrJTAG since it is mainly used for debugging. But it can be also used for debricking.

-

http://openocd.sourceforge.net/

-

Debricking AR71xx

Зачем нужен JTAG

Самый большой плюс в JTAG — это возможность внутрисхемного программирования микросхем памяти ресиверов. С его помощью восстанавливать потерянное или испорченное содержимое флэш-памяти, при этом не выпаивая микросхем и без необходимости использования программаторов. То есть JTAG нужен именно тогда, когда неисправен загрузчик, что делает невозможным заливку ПО штатным способом.

Минусом является тот факт, что интерфейс JTAG, в большинстве своём, на всех ресиверах разный — единый стандарт существует, но каждый производитель его модифицирует по-своему. Globo X90 работает на процессоре ALI 3329С.

Прошивка через JTAG куда сложней обычной процедуры, поэтому к ней прибегают только в самом крайнем случае, когда ресивер совсем не подаёт признаков жизни: не загружается, не горит индикация, прошили другой прошивкой, либо после прошивки у вас только черный экран

JTAG прошивка по шагам

Для того, что бы запрограммировать флэш ресивера с помощью JTAG кроме собственно «пациента», т.е. ресивера, который нам необходимо «оживить», нам нужно иметь следующее:

1. Собрать интерфейс (переходник) от порта ресивера к порту ПК

Собрать адаптер для JTAG не так сложно, как кажется на первый взгляд. Для Globo X90, да и вообще для всех ресиверов, предпочтительным вариантом сборки является вариант на микросхеме 74HC244N (её еще называют даташит). Распиновка JTAG:

Так выглядит собранная схема:

Со стороны ресивера это будет специальный разъём, он иногда даже так и подписан — JTAG

Второй «конец», который уходит в сторону ПК — это обычный LPT-кабель, который можно купить в любом компьютерном магазине. О том, как можно собрать всё это хозяйство:

2. Найти LPT-порт на ПК

Параллельный порт на компьютере сейчас можно увидеть только в музее, поэтому можно докупить специальный LPT-PCI контроллер, который позволяет подключить ваш JTAG к системному блоку ПК, у которого нет LPT порта (а это будет в 99,9% случаев).

5. Скачиваем прошивку

Нужна сама прошивка, т.е. то, что мы будем заливать во Flash-память. Здесь есть два варианта

- Только загрузчик (лоадер) — файл с расширением .bin. это та часть содержимого флэш ресивера, которая обеспечивает загрузку в него ПО(софта) через порт. Если мы имеем случай, когда нам для заливки нужен только загрузчик(лоадер) ресивера, то поступаем одним из двух способов – или скачиваем готовый файл с загрузчиком, или делаем его самостоятельно. Для этого в HEX-редакторе отрезаем от файла ПО первые 65536 байт и сохраняем как отдельный файл *.bin. Это и есть загрузчик.

- Полный дамп. Дамп для JTAG, в случае, с ресиверами Globo — это обычный дамп, который используется для прошивки. Единственное, необходимо будет сменить расширение файла с *.abs на *.bin

6. Переводим ресивер в отладочный режим

Для прошивки также потребуется перевод ресивера в режим отладки, он же Debug Mode. Способы его перевода зависят от конкретной модели приставки, конкретно для Globo X90 cсоединить (замкнуть) перемычкой предназначенные для этого контактные площадки на плате, где стоит обозначение JP1. Так же бывает, что надписи JP1 на ресивере нет, тогда нужно выпаять резистор R32

Обратите внимание на точки подключения. Они должны совпадать с тем, как вы собрали переходник

В некоторых Globo-ресиверах бывает обратная последовательность — не перепутайте. На некоторых ресиверах можно сделать обычную перемычку для перевода в отладочный режим

Можно использовать перемычку с IDE-винчестеров

Так это будет выглядеть:

7. Настраиваем EJTAG и прошиваем

Настройки в нашей JTAG tool выставляем так же как на скриншоте:

Если EJTAG не увидит ресивер, попробуйте поменять тип флеш памяти в последнем столбике. Вообще, здесь можно пробовать менять любые параметры, чтобы ресивер определился

В некоторых мануалах пишут, что предварительно нужно стирать флеш — делать этого не стоит, ни поблочно, ни полностью, перед записью программа сама сотрёт столько памяти, сколько ей надо записать, она умеет это делать. Далее жмём «коннект». В окне программы должен побежать текст лога.

Если после нажатия кнопки «коннект», у вас выходит ошибка «флэш ID нету в *.ini –файле», то попробуйте поменять настройки в программе, как и советовали выше, нужно попробовать все вариации галочек и точек в настройках. Если и это не приведет к успеху, то тут стоит насторожиться — проверить питание процессора, напряжение с БП — есть вероятность того, что флеш-память уже «умерла», тогда никакой JTAG уже не поможет. Следующим шагом жмём «Записать» и в окне проводника выбираем нужный файл с дампом или загрузчиком (лоадером)

При необходимости, как мы и писали выше, EJTAG сотрёт самостоятельно нужный блок памяти и начнет запись.

Здесь есть небольшой нюанс — достаточно залить около 50-70% прошивки через JTAG (желательно, конечно, полностью), но если у вас оборвалась прошивка на этом этапе, то можно попробовать прошивать стандартно (через порт), т.к. дальше уже идут списки каналов, спутники и так далее, т.е. то, что вы зальете и обычный прошивкой.

8. Убираем перемычку, отключаем Debug Mode

Не забудьте в конце прошивки корректно завершить программу EJAG, отключить от сети ресивер и аккуратно отключить JTAG-интерфейс. Так же снять перемычку для входа в отладочный режим. Далее подключаем ресивер уже через ком-порт и заливаем в него софт обычным способом.

JTAG в каждый дом: полный доступ через USB +57

- 08.11.17 02:44

•

ptsecurity

•

#341946

•

Хабрахабр

•

•

14100

Информационная безопасность, Блог компании Positive Technologies

Исследователи Positive Technologies активировали аппаратную отладку (JTAG) для Intel Management Engine, которая позволяет получить полный доступ ко всем устройствам PCH (Platform Controller Hub), используя технологию Intel DCI (через интерфейс USB). Мы планируем поделиться подробностями на одной из ближайших конференций. А о том, как активировать этот интерфейс, но для основного процессора, расскажем ниже.

От ошибок никто не застрахован. Это утверждение касается и низкоуровневого программирования, где таких привычных средств, как отладочная печать или программный отладчик, в определенный момент может быть уже недостаточно. Для решения этой проблемы разработчики аппаратных средств используют так называемые внутрисхемные эмуляторы (in-circuit emulators) или специальный отладочный интерфейс JTAG, если он присутствует на целевой платформе (IEEE1149.1 ). Эти отладочные механизмы появились еще в 80-х годах прошлого века . Со временем производители микросхем расширяли возможности этих интерфейсов. Благодаря этому разработчики смогли получать детальную информацию об энергопотреблении, находить узкие места в высокопроизводительных алгоритмах и получили много других возможностей.

Для исследователей безопасности аппаратные средства отладки также представляют интерес. Они позволяют получить низкоуровневый доступ к системе в обход основных средств обеспечения безопасности, изучать поведение целевой платформы и ее недокументированные возможности. Очевидно, что подобные возможности оказались привлекательны и для спецслужб .

Долгое время доступ к этим технологиям для процессоров Intel имелся только у ограниченного круга лиц, что было связанно с необходимостью использования дорогого специализированного оборудования. Но с выходом процессоров семейства Skylake ситуация кардинально изменилась: отладочные механизмы были встроены в PCH , что позволяет использовать столь мощный инструмент обычным пользователям — включая и злоумышленников, которые могут таким образом получить полный контроль над процессором. Из соображений безопасности по умолчанию эти механизмы не активированы, но в данной статье мы покажем, что их можно заставить работать на оборудовании, которое доступно в обычных компьютерных магазинах.

Инструкция на английском языке для восстановления мобильного устройства SAMSUNG GT-i9100, приведенная в RIFF JTAG менеджере

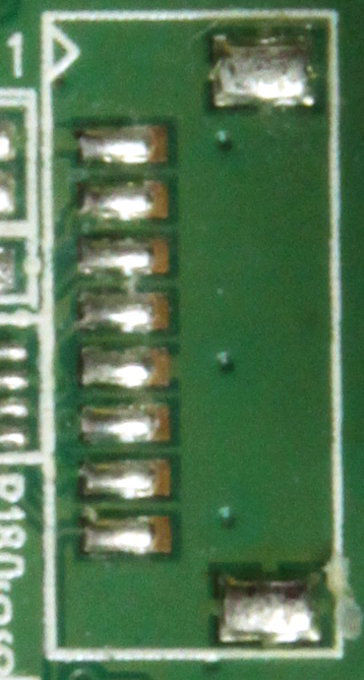

Samsung I9105 is based on the Broadcom BCM28145 Processor (Cortex-A9 Dual-Core). JTAG pads are very small; professional experience in soldering is required to connect wires to the JTAG interface.

Note, one simple way to connect over JTAG — connect USB cable to PC and insert battery. In this case phone is automatically powered on.

To resurrect Samsung I9105:

- Solder JTAG cable to Samsung I9105 JTAG pads.

- Connect USB cable to phone and PC.

- Insert battery.

- Make sure Samsung I9105 is selected in the list of models.

- Make sure a fixed TCK frequency is selected.

- Click Resurrect button.

- Wait for software to complete operation successfully.

- Disconnect USB cable, de-solder JTAG wires.

Now phone is in bootable condition, that is, even if it does not start up normally, you can flash it using original Samsung downloader software to restore it to the working state.

To enter download mode:

- Disconnect PC cable.

- Insert battery.

- Hold both ‘Volume Down’ and ‘Home’ keys and press Power-On.

Most common errors:

- The NRST signal is not connected. Pease ALWAYS SOLDER THE NRST SIGNAL whenever it is present on the schematics. In case you have JIG please make sure NRST is routed, if not — solder wire manually.

- Connection is unstable or cannot be established at all. Please make sure JTAG wires are of the SAME LENGTH and total length of each wire not exceeds ~10…15 cm; make sure a fixed TCK frequency is selected (since device has no RTCK signal).

Загрузка файла конфигурации в микросхему ПЛИС

В первую очередь стоит разобраться с режимом загрузки ПЛИС. Для тех, кто только начинает знакомится с темой, проведу маленький экскурс. Хотя на моей плате установлена ПЛИС Altera (Intel) семейства Cyclone IV E, методы загрузки аналогичны для всей группы ПЛИС Cyclone, и есть подозрение, что в том или ином виде подходят для многих других семейств.

В ПЛИС данного типа используется энергозависимая SRAM для хранения конфигурационных данных. Эти конфигурационные данные определяют функционал итогового устройства. На профессиональном жаргоне эти данные часто называют «прошивкой». Таким образом, прошивка хранится в специальном ОЗУ и каждый раз при включении устройства должна быть загружена в кристалл ПЛИС. Существует несколько способов (схем конфигурации), которыми прошивка может быть загружена в SRAM (список актуален для Cyclone IV E):

- Активный последовательный (Active serial (AS)).

- Активный параллельный (Active parallel (AP)).

- Пассивный последовательный (Passive serial (PS)).

- Быстрый пассивный параллельный (Fast passive parallel (FPP)).

- JTAG.

Выбор конкретного режима загрузки выполняется с помощью внешних выводов ПЛИС (группа MSEL). Режим JTAG доступен всегда. Активный режим подразумевает, что при подаче питания ПЛИС самостоятельно вычитывает данные из внешней памяти (последовательной или параллельной). В пассивном режиме ПЛИС ждет, когда внешний носитель в инициативном порядке передаст ей данные конфигурации. Данные схемы хорошо укладываются в концепцию ведущий (Master) — ведомый (Slave). В активных режимах ПЛИС выступает в качестве ведущего, а в пассивных — в качестве ведомого.

В рассматриваемой задаче не ПЛИС, а пользователь должен решать, когда должна обновляться прошивка, поэтому режим загрузки должен быть пассивным. А для экономия ножек микросхемы выбираем последовательный интерфейс. Здесь подходит пассивный последовательный (PS) режим и JTAG. Логика работы JTAG несколько сложнее, поэтому остановимся на первом варианте.

Ниже на рисунке показана схема подключения ПЛИС к внешнему контроллеру для загрузки в режиме PS.

Для начала конфигурации внешний ведущий контроллер должен генерировать переход из низкого уровня в высокий на линии nCONFIG. Как только ПЛИС будет готова к приему данных, она сформирует высокий уровень на линии nSTATUS. После чего ведущий может начать передавать данные по линии DATA, а соответствующие тактовые импульсы — по линии DCLK. Данные должны передаваться в целевое устройство до тех пор, пока на линии CONF_DONE не установится высокий уровень (или данные не закончатся), при этом ПЛИС перейдет в состояние инициализации. Следует учесть, что после того как CONF_DONE установилась в единицу, нужно подать еще два тактовых импульса, чтобы началась инициализация ПЛИС.

Данные передаются младшим значащим разрядом (LSB) вперед, то есть, если конфигурационный файл содержит последовательность 02 1B EE 01 FA (пример взять как есть из Handbook), на линии данных должна быть сформирована последовательность:

Таким образом, используется всего пять линий: линии DATA и DCLK — для последовательной передачи, линии nCONFIG, nSTATUS, CONF_DONE — для управления.

По своей сути режим PS есть не что иное, как SPI с дополнительной манипуляцией флагами.

Скорость передачи данных должна быть ниже указанной в документации максимальной частоты, для используемой в проекте серии Cyclone IV E — это 66 МГц.

Минимальной же частоты передачи не существует, теоретически можно приостановить конфигурацию на неопределенное время. Это дает отличные возможности пошаговой отладки с участием осциллографа, чем мы непременно воспользуемся.

На рисунке ниже показана временная диаграмма интерфейса с наиболее значащими таймингами.